SYSTEM CASCON

The quality of Embedded JTAG Solutions is significantly determined by the performance and architecture of the used software. SYSTEM CASCON™ is a software platform with comprehensive tools for automated test program generation.

To perfectly address the needs of development, production and customer service, the software packages are available for In-system-programming (ISP) with CASCON POLARIS and ISP and test methods with CASCON GALAXY

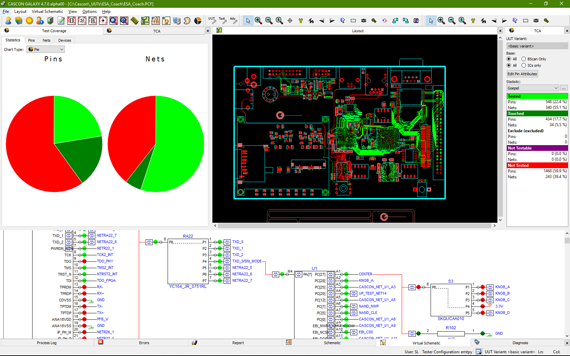

Test Coverage Analyzer for higher test coverage

The Test Coverage Analyzer is a powerful tool in SYSTEM CASCON Version. With numerous details, test reports are far beyond simple JTAG/Boundary Scan test reports. The TCA provides improved information about which nets and pins have been tested sufficiently and which have not.

More Info

The TCA tool in SYSTEM CASCON offers you an optimal approach for analyzing the test coverage of the DUT. This allows you to effectively identify problem areas (e.g. due to insufficient tests) or possible time savings (e.g. due to too many tests).

By using filters and switchable templates for test group definitions, you can change the focus of the analysis at lightning speed. With just a few clicks you can find out not only what was tested, but also how.

Test Coverage Analyzer Highlights

- Test Group definition: You can define exactly when an element is considered tested and which attributes are required for it.

- Extended TCA attribute base: Characteristics such as Level (High/Low), Direction (In/Out) or Speed (Dynamic, Static, Functional, Stress) allow you to see at any time how extensively an element has been tested.

- Inclusion of Emulation Technologies: VarioTAP, ChipVORX/SI, JEDOS and other technologies are now being mapped the new TCA

- Improved reports through neighborhood analysis: The neighborhood of an element is identified and analyzed. This significantly increases test coverage accuracy. For example, short circuits are only observed between adjacent pins.

- Comparison of test coverage results: You can see directly what contribution the different test programs make to test coverage.

- Import of external test coverage information: Use information from other test systems (e.g. flying probe tester, in-circuit tester) or inspection systems (e.g. AOI, AXI or SPI) for analysis and get more detailed information about the test coverage of your board.

- Hierarchical visualization: You can adjust the degree of clarity or detail at any time.

Webcast Download

Register now and view the current webcast!

► New options in SYSTEM CASCON 4.7

(2020-04-09)

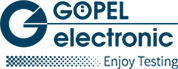

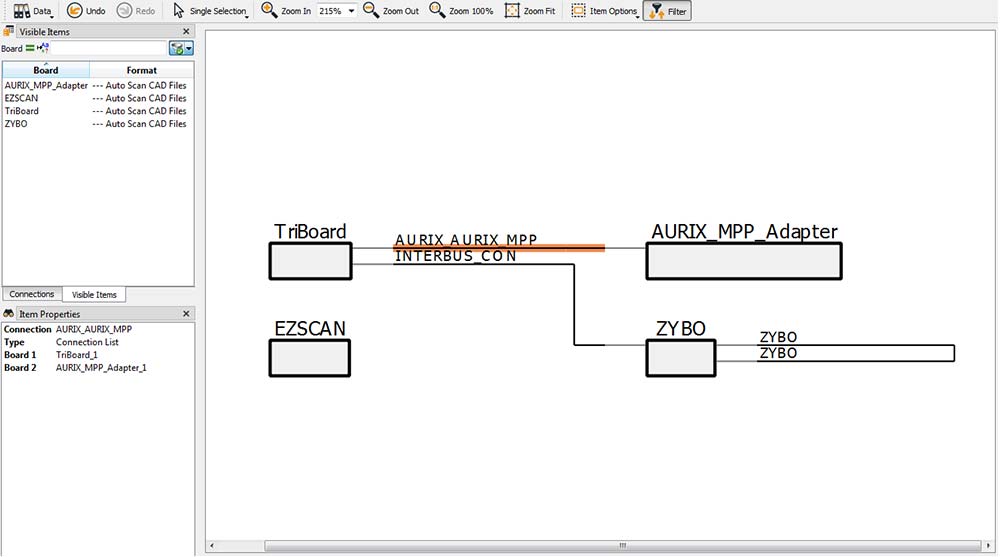

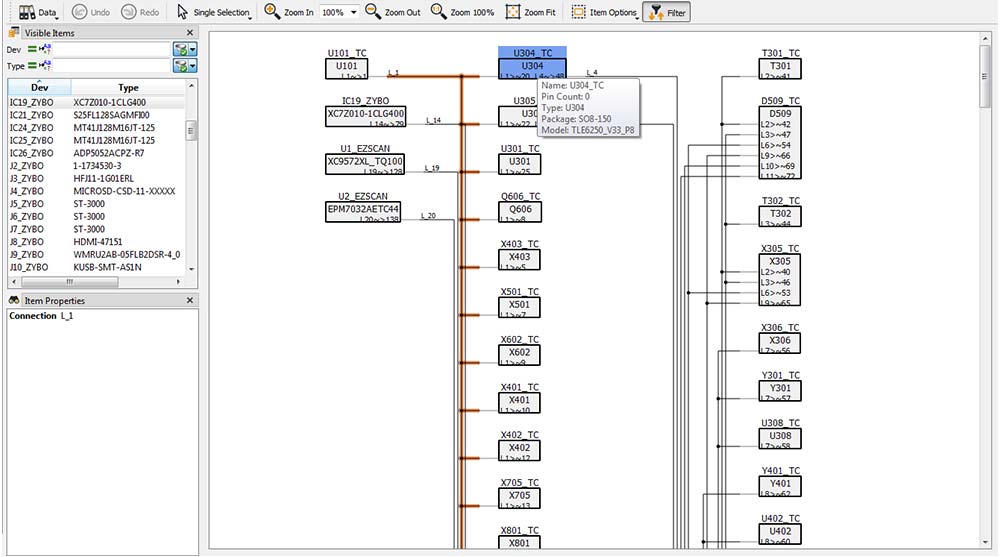

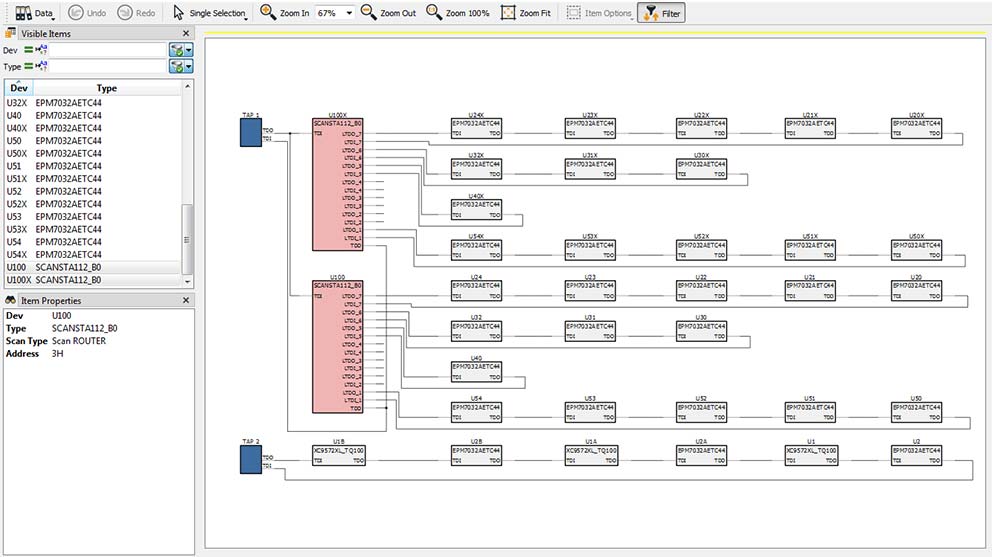

ViPX - Visual Project Explorer - Clear Overview

In the age of ever larger and more complex projects, new approaches for presentation, analysis and interaction are needed. The Visual Project Explorer (ViPX) in SYSTEM CASCON is your long-awaited tool. The viewer presents complex board and test information in a simple way. You can analyze networks in detail and interact with all elements. Only the information you really need is displayed.

Webcast Download

Register now and view the current webcast!

► Next Generation CASCON GUI: Visual Project Explorer

(2019-12-03)

The highlights of ViPX

- central user interface

- direct triggering of processes from the graphical user interface

- visualization of board data and mirroring of test and additional information (e.g. test coverage)

- graphical interaction at all levels (system and board level, scan path display, device network level)

- real, graphical elements instead of lists, input masks and tables

With ViPX all information is easily manageable. This also includes the display of logical interconnections beyond board boundaries. This is especially interesting if your device under test consists of several interconnected boards. See only the information you want to see - and hide those you don't need.

Emulation Based Interconnection Test – EmuBIT

Test them All! - the automatic interconnection test also reaches non-boundary-scan capable pins

An automatic connection test, the so-called Emulation Based Interconnection Test, considerably increases the test coverage of your board: by automatically integrating your microcontrollers, which are not boundary-scan capable at all.

EmuBIT utilizes the modules of a microcontroller, making the device a reliable test instrument. It emulates a boundary-scan structure in the chip, so that many pins of the microcontroller - especially the GPIO ports (General Purpose In Out ports) - can be used in the same way as with boundary scan. This automatically integrates the microcontroller into the connection test together with other boundary scan devices.

The Emulation Based Interconnection Test is based on the VarioTAP technology.

Contact

Contact