# Building bridges between development and production of electronic PCBs or Boards: Solutions for typical chicken-and-egg problems

The rapid development of the electronics industry has produced a multitude of innovations that have a significant impact on our daily lives. From powerful smartphones to smart home appliances and autonomous vehicles, electronic devices have fundamentally changed the way we communicate, work and live. But behind every groundbreaking product is a complex process of product development and production.

Continuous advances in microelectronics and semiconductor technology make it possible to produce ever more powerful and miniaturised components. This allows more functions to be integrated in a limited space, which increases the complexity of electronic PCBs or Boards. Artificial intelligence (AI) and machine learning in electronic devices opens up new possibilities and applications. However, AI requires powerful processors and elaborate algorithms, which further increases the complexity of electronic PCBs or Boards.

In the world of electronics manufacturing, we encounter tricky tasks again and again. Two processes in particular often seem to be subject to the typical chicken-and-egg problem: development and production. When developing new products, numerous factors have to be taken into account, including design, material selection or various performance parameters. At the same time, production facilities and processes must be adapted to the specific requirements of the product in order to enable efficient and high-quality manufacturing. However, optimisation goals or requirements of both sides are often at odds with each other. Or data is required without which further development of the product or manufacturing process is not possible. But where should this data come from if neither the design of the product nor production processes are finally defined? We examine the central challenges that arise during the transition from development to production and present proven strategies and tools that enable a smooth synchronisation of both processes.

#### Embedded test functions

The first typical chicken-and-egg problem concerns the basic design of the product. At the beginning of the development process, the choice of materials plays a major role. In addition to factors relating to the performance of the components used, availability and, of course, price are also decisive. However, beginning with the selection of the components to be used, attention should be paid to suitable testability.

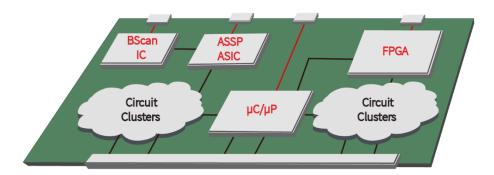

Most microcontrollers, FPGAs or CPLDs, which are at the heart of every electronic design, support the so-called IEEE1149.1 test standard, which is better known as Boundary Scan. This enables extensive test possibilities with only a few access points, the typical JTAG signals. In addition to the basic possibility of controlling and measuring signals, functional test functions, such as the evaluation of a

Press Contact:

GÖPEL electronic GmbH Christina Schellbach Göschwitzer Straße 58/60 07745 Jena, Germany

Tel.: +49 (0)3641-6896-739 Fax: +49 (0)3641-6896-944 E-Mail: presse@goepel.com Web: www.goepel.com

component identification or the control of various sensors, can also be realised. Basic test functions thus become an integral part of the product design, which considerably reduces external test equipment and complex adaptations.

Fig. 1: Available Embedded Instruments

In addition to the classic test options of boundary scan, which are traditionally used for static connection and simple function tests, this access can also be used for additional emulation technologies. For example, instruments of the microcontroller can be addressed, parameterised and used for test purposes via the same JTAG signals or other debug interfaces. Special FPGA designs are suitable for complex test tasks such as frequency measurement or bit error rate tests.

GÖPEL electronic GmbH calls this use of test functions, embedded natively in the design, the Embedded JTAG Solutions (EJS). This term covers all instruments as well as their application possibilities for testing and programming. With the help of the common software platform SYSTEM CASCON, all access can be realised. Hardware specially adapted to the requirements of development and production (e.g. SCANFLEX II CUBE) enables seamless use of created procedures in both application areas. Production and development use the same tools for prototype tests, initial commissioning and production tests.

## Optimisation of the design

Electronics developers are often confronted with optimisation processes. The focus is particularly on minimising electronic designs. In particular, a reduction of test points is essential. Test engineers on the other hand need access points to verify critical component sizes, signals or functions. This dilemma leads to iterations of the design. Designers depend on input from production to find out where the design can be reduced without reducing test coverage. Test engineers, however, need detailed design data from development for this analysis.

The Test Coverage Analyzer in SYSTEM CASCON enables an early estimation of the achievable test depth and thus provides useful data for development. No ready-designed layouts or even ready-produced PCBs or Boards are required. A network and component list is sufficient for an initial evaluation of the design. After appropriate modelling, the software already calculates possible test

# Press Contact:

GÖPEL electronic GmbH Christina Schellbach Göschwitzer Straße 58/60 07745 Jena, Germany

Tel.: +49 (0)3641-6896-739 Fax: +49 (0)3641-6896-944 E-Mail: presse@goepel.com

Web: www.goepel.com

functions and determines test coverage on this basis. At this early stage, these data allow for an indepth analysis and thus provide clues for optimisation possibilities.

As an example, let us consider the topic of reducing test points. Using the test coverage analysis that has already been created, it is possible to look at the signal level to see whether test opportunities exist. Basically, the system only assumes the embedded instruments and initially ignores possible access via test points. If the signal is marked as tested, a corresponding test point can probably be saved. The following figure illustrates this.

| Dev | Port | #Pin | Net     | Туре    | TCA Statistic  | OutCell | InCell | CtrlCell |

|-----|------|------|---------|---------|----------------|---------|--------|----------|

| TP1 |      | 1    | BSN6    | In      | Not Tested     |         |        |          |

| U2  | IN40 | 40   | BSN6    | In      | Tested Connect |         | 90     |          |

| U4  | Y2   | 6    | BSN6    | Out     | Tested Connect |         |        |          |

| U5  | OE3  | 10   | BSN6    | In      | Tested Connect |         |        |          |

| Dev | Port | #Pin | Net     | Туре    | TCA Statistic  | OutCell | InCell | CtrlCell |

| R16 |      | 2    | BSN12   | Linkage | Not Tested     |         |        |          |

| U5  |      | 11   | BSN12   | Out     | Tested Connect |         |        |          |

| R16 | Y4   | 1    | N310249 | Linkage | Not Tested     |         |        |          |

| TP3 |      | 1    | N310249 | In      | Not Tested     |         |        |          |

| U5  | Y3   | 8    | N310249 | Out     | Tested Single  |         |        |          |

| U2  | 1027 | 27   | BSN12   | InOut   | Tested Connect | 26      | 24     | 25       |

Fig. 2: TP analysis based on test coverage (top: TP1 can be reduced, bottom: TP3 increases test coverage)

All elements of the signal BSN6 have been marked as tested (green). Only the test point TP1 is not used (red). It can therefore be removed without concern. With signal BSN12, however, the resistor R16 cannot be tested. However, this test would be possible through an external adaptation TP3. Removing the test point would therefore reduce the test coverage.

However, these analysis and optimisation possibilities do not only concern the reduction of test points, but also the basic design. Does a pull resistor perhaps already prevent the activation of the embedded test function? Can an alternative placement of a component significantly improve the production processes due to more suitable test instruments? Many of these questions can be answered at an early stage with the help of the Test Coverage Analyzer.

#### Process optimisation

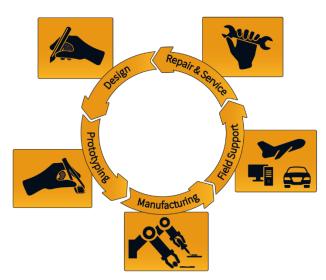

Production processes are also subject to continuous optimisation tasks. Efficiency, throughput and, of course, quality must be constantly increased. Our chicken-and-egg problem occurs when processes are defined early on and late design changes lead to inefficient or even incompatible systems. However, to ensure the smoothest and most timely transition from development to production, manufacturing processes must be developed early on.

Web: www.goepel.com

Approval status: approved

Fig. 3: Electronics development process cycle

EJS can bridge the gap between development and production. The same tools are available to both areas. This means that procedures and functions that have already been developed and put into operation can easily be transferred from development to production. Hardware developers thus get a tool with which they can address, verify and also programme their prototypes without special test firmware. At the same time, these functions can be adapted directly for the test system without any necessary adjustments. The test or process engineer can concentrate exclusively on integrating the functions into the production process. The effort after development cycles is thus also reduced, since the function has already been verified on the part of the development.

The extensive possibilities of EJS can also relieve other test systems. The in-circuit test (ICT) can be reduced to relevant components because the EJS test could more efficiently generate a high test coverage. Functional tests from the End-Of-Line (EOL) test can also be placed earlier in the production process, for example if repairs are still possible in the event of a fault. There is also no need for highly specialised test equipment because all the necessary instruments are a native part of the electronic PCB or Board.

By redistributing test solutions to EJS, cycle times can be reduced, diagnostic capabilities improved and costs reduced. In addition, existing production lines and test systems can be equipped with the integration packages of GÖPEL electronic GmbH and thus EJS test capabilities can be added. No costly reconstruction of the production line is required. Integration packages exist for ICT, Flying Prober and EOL tester, whereby test resources interactively combined ensure the best possible test coverage.

#### Conclusion

Close collaboration between development and production is crucial to successfully realising state-of-the-art products and processes. The use of embedded tools and the implementation of the EJS testing

### Press Contact:

GÖPEL electronic GmbH Christina Schellbach Göschwitzer Straße 58/60 07745 Jena, Germany

Tel.: +49 (0)3641-6896-739 Fax: +49 (0)3641-6896-944 E-Mail: presse@goepel.com Web: www.goepel.com

strategy have proven to be highly effective methods to achieve this goal. These advanced approaches bring both departments closer together and allow them to exploit synergies to increase product efficiency and quality.

The close integration of development and production through embedded tools and the EJS test strategy also leads to improved communication and a better understanding of the requirements and capabilities of both departments. Through the regular exchange of data and insights, bottlenecks or challenges can be identified at an early stage and jointly overcome. This avoids potential conflicts and ensures a smooth integration of product design and manufacturing processes.

#### Author:

Alexander Labrada Diaz, Application Engineer in the Embedded JTAG Solutions Division at GÖPEL electronic GmbH