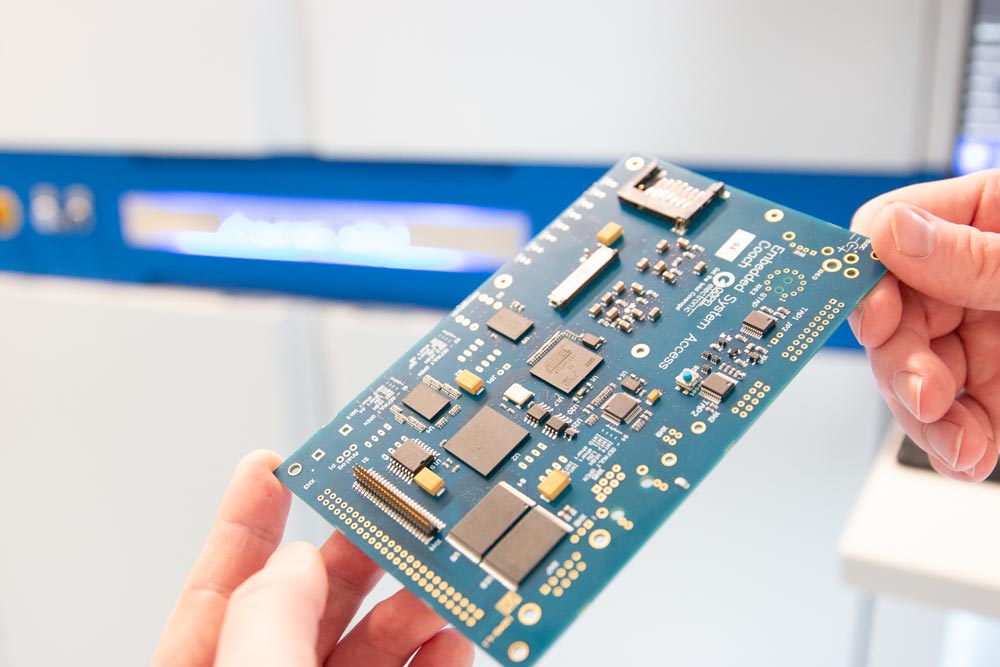

Weitere Dienstleistungen im Service-Bereich

Testprogrammerstellung, Schulungen und Seminare sind nur einige von vielen Aufgabenstellungen, mit denen unser Supportteam täglich konfrontiert wird. Das Serviceteam der GÖPEL electronic unterstützt Sie z.B. auch bei der BSDL-Verifikation, bei der Kalibrierung bestimmter Hardware-Module und bei allen anderen Fragen rund um das Thema "Test & Programmierung via JTAG & Boundary Scan".

Gemeinsam finden wir eine effiziente Lösung, die zu Ihnen und Ihrer Applikation passt.

Die folgenden Dienstleistungen können u.a. in Anspruch genommen werden:

-

Modellerstellung für Nicht-Boundary-Scan-fähige ICs

-

BSDL-Verifikation

-

Testabdeckungsanalyse

-

Workshop an Ihrer Applikation

-

Test von Prototypen-Baugruppen bis hin zu Kleinserien

-

Programmierung von Prototypen-Baugruppen bis hin zu Kleinserien

-

Analyse der Testprogramm-Performance – Reduzierung Test-/Programmierzeit

-

Kalibrierservice für Ihre Hardware-Module von GÖPEL electronic (mit CION LX ICs)

- Röntgendienstleistung

Kontakt

Kontakt