# **Boundary Scan meets Funktionstest**

Thomas Wenzel, Enrico Zimmermann (GÖPEL electronic)

Eines der gravierendsten Probleme im Bereich des Testens ist der kontinuierlich sinkende physikalische Zugriff. Über verschiedene Märkte hinweg berichten Anwender unisono hier von bis zu 20% Einbrüchen innerhalb der letzten 5 Jahre was zwangsläufig zu Diskussionen über zukünftig anwendbare Testmethoden führt. In diesem Kontext hat sich JTAG Boundary Scan einen guten Namen erarbeitet, allerdings kann auch dieses Verfahren nicht alle Probleme lösen und braucht Partner. Dabei steht vor allem der Funktionstest im Mittelpunkt des Interesses. Der vorliegende Beitrag analysiert einige Grundlegende Aspekte dieser Kombination und stellt neue technologische Lösungsansätze für eingebettete Funktionstests, sowie ihre praktische Umsetzung vor.

### **Im Spannungsfeld von Struktur und Funktion**

Egal welche der bekannten elektrischen Teststrategien man sich anschaut, sie alle lassen sich in zwei grundlegende Kategorien einordnen – Strukturtest und Funktionstest. Beide verfolgen gemäß Tab. 1 völlig unterschiedliche Prinzipien um Fehler zu stimulieren und zu diagnostizieren. Während der Strukturtest versucht das Design durch Zugriff auf Elementarebene zu testen, zielt der Funktionstest auf die Prüfung zusammenhängender Schaltungsteile ab.

| Testkategorie | Grundlegendes Wirkprinzip                                                                                                                                                                                                                                           | Typisches Equipment                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Strukturtest  | <ul> <li>Test der strukturellen Integrität einzelner oder<br/>mehrerer unabhängiger Verbindungen, bzw.<br/>Signalpfade</li> <li>Messung einzeln isolierter Komponenten</li> <li>Fehlerdiagnose durch Auswertung dedizierter<br/>Vektoren, bzw. Messungen</li> </ul> | <ul><li>Manufacturing Defect Analyzer</li><li>Flying Prober</li><li>In-Circuit Tester</li><li>JTAG Boundary Scan</li></ul> |

| Funktionstest | <ul> <li>Test der Gesamtschaltung, oder einer<br/>Teilschaltung (Cluster) mit einer Folge von<br/>Vektoren, bzw. analogen Waveforms</li> <li>Fehlerdiagnose durch Auswertung der<br/>Response-Vektoren, bzw. Waveforms</li> </ul>                                   | <ul><li>Funktionstester</li><li>Clustertester</li><li>Emulationstester</li><li>Muttermaschinen-Tester</li></ul>            |

Tab.1: Charakterisierung grundlegender Testprinzipien

Allerdings bedingt der Strukturtest für seinen Erfolg auch die Absicherung des notwendigen Elementar-Zugriffs und hier können Techniken wie ICT, MDA oder FPT immer weniger punkten. Der Funktionstest dagegen benutzt typischerweise die nativen Anschlüsse einer Unit Under Test (UUT) als Zugriffsbasis und umgeht somit diese Problematik.

Daher ist es auch kein Wunder, dass diese Technik wieder verstärkt im Fokus der Anwender steht. Eine Untergruppe des Funktionstests ist der sogenannte Clustertest. Clustertests sind im Grunde genommen das Resultat mangelnden Zugriffs, denn sie beinhalten den Test einer Teilschaltung über die am Rand der Partition zur Verfügung stehenden Testpunkte. Schwindender Testzugriff führt daher in der logischen Konsequenz zu immer größeren Clustern bis hin zum vollständigen Verlust sinnvoller Clusterbildungen.

Ein immer wieder Heiß diskutiertes Thema ist auch die Fragen ob der Strukturtest nun den Funktionstest überflüssig macht oder umgekehrt. Dahinter versteckt sich vor allem der Wunsch möglichst wenig zu testen, denn das kostet Geld und wenn es denn unvermeidlich ist sollte man sich vorteilhafterweise wenigstens auf eine primäre Methode festlegen.

Um diese Frage zu beantworten spielen einige grundsätzliche Faktoren eine Rolle, welche nachfolgend diskutiert werden.

Ein Strukturtest kann auf elektrisch-physikalischer Ebene das Vorhandensein der Integrität einer Schaltung nachweisen. Die Tests sind typischerweise überwiegend statischer Natur, teilweise at-speed. Er kann in diesem Rahmen auch präzise Fehlerdiagnosen liefern. Er prüft jedoch keine Funktion, kann also ein Fehlverhalten der Schaltung im Betriebsmode nicht erkennen. Das limitiert die Fehlerabdeckung, gemessen am Gesamtspektrum möglicher Fehler. Damit eignen sich Strukturtests hervorragend als indirekte Prozesssensoren, sie ersetzten jedoch mitnichten den Funktionstest.

Der Funktionstest wiederum bietet prinzipiell eine hohe Fehlerabdeckung und er kann auch Anomalien im Betriebsmodus erkennen, vorausgesetzt er wird mit der entsprechenden Dynamik durchgeführt. Das hängt aber auch sehr stark von den eingesetzten Testmustern ab, denn Fehler müssen zur Erkennung auch stimuliert werden. Sofern sich strukturelle Fehler auch auf die Funktion auswirken kann er diese auch erkennen, allerdings sind die Fehlerdiagnosen sehr verwaschen. Werden strukturell vorhandene Fehler nicht funktional stimuliert entsteht generell ein Fehlerschlupf, welcher später schwerwiegende Konsequenzen haben kann. Davon betroffen sind auch parametrische Fehler an diskreten Bauelementen, offene Pins mit floatendem Signalpegel, fehlende Pull-Widerstände oder nicht korrekt montierte Stützkondensatoren um nur einige Probleme zu nennen. Damit sind Funktionstests in der Produktion prädestiniert für einen grundlegenden Nachweis der Erfüllung ausgewählter Betriebsmodi wie sie z.B. im End-of-Line (EoL) Test erfolgen, sie sind aber mitnichten ein Ersatz für den Strukturtest.

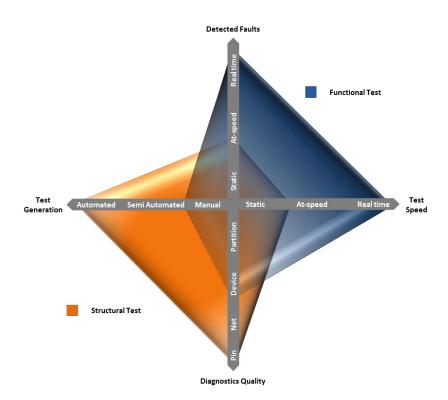

Abb.1: Leistungs-Potential ausgewählter Eigenschaften von Struktur- und Funktionstest

Eine tendenzielle Darstellung grundlegender Faktoren wie sie in Abb. 1 enthalten ist, macht die Stärken und Schwächen der beiden Strategien plastisch. Dabei wird anschaulich, dass der Strukturtest und der Funktionstest eine hervorragende Synergie besitzen und keinesfalls alternativ betrachtet werden sollten. Der richtige Weg das volle Potential dieses Duos zu erschließen liegt vielmehr in der Kombination.

## Standardisierte Vielfältigkeit

Obwohl JTAG Boundary Scan mittlerweile schon über 25 Jahre als IEEE1149.1 Standard existiert [1], haben ihn die zyklisch vorgenommenen Erweiterungen wie z.B. IEEE1149.6 [2] und neue Releases [3] beständig auf Höhe der technologischen Anforderungen und damit jung gehalten. Im Zusammenhang mit dem hier diskutierten Thema sollen einige Eigenschaften jedoch besonders herausgehoben werden:

Der Standard wurde als Nachfolger des digitalen, statischen In-Circuit-Tests konzipiert, darüber hinaus gehende Bereiche kann er nur schwer oder gar nicht abdecken

- JTAG Boundary Scan definiert lediglich digitale Testpunkte innerhalb von Chips, diese sind sowohl für den Strukturtest, als auch für statischen Funktionstest nutzbar

- Da der innere Schaltkreiskern bei aktivem Testmode quasi isoliert wird, gelingt in genialer Weise die grundsätzliche Trennung von Funktion und Struktur.

- Die hohe Automatisierbarkeit der Testvektorgenerierung sichert gleichzeitig auch die hohe Diagnosequalität. Hier zeigt das Verfahren eine fast unschlagbare Effektivität.

- Die Fehlerabdeckung ist im Voraus kalkulierbar, d.h. Designs können noch in der Testbarkeit optimiert werden bevor ein physikalischer Prototyp gebaut wird.

- Die Fehlerabdeckung wird im digitalen Bereich primär durch die begrenzte Vektorfolgefrequenz limitiert, kann also keine dynamischen Fehler erkennen.

Boundary Scan hat sich sinnvollerweise vor allem in den komplexen Chips, wie Prozessoren, FPGA, DSP und ASIC etabliert. Bereits ein Boundary Scan Schaltkreis kann hervorragende Dienste beim Testen erzielen [4] und ist im Verbund mit Inspektionstechnologien auch eine sinnvolle Ergänzung als Prozesssensor [5].

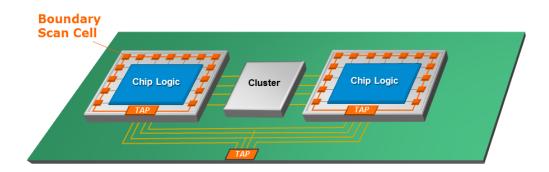

Eine Möglichkeit der Nutzung von Boundary Scan zum Funktionstest ist durch den Clustertest gegeben (Abb.2).

Abb.2: Funktionaler Clustertest per Boundary Scan

Es gibt sehr vielfältige Spielarten wie ein Clustertest aussehen kann. Zur weiterführenden Erklärung sei an dieser Stelle auf die Literatur verwiesen [4].

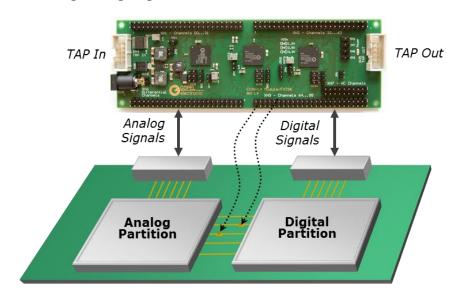

Neben solchen eingebetteten Applikationen können auch externe I/O Module zum Einsatz kommen (Abb.3). Sie sind in der Lage eine Gesamtschaltung einfach über die nativen Steckverbinder statisch funktional ansteuern, oder auch über Testpunkte auf der UUT. Sind weitere Boundary Scan Schaltkreise auf dem Board können oftmals auch tiefe strukturelle Tests von Steckverbindern oder anderen nicht scanfähigen Partitionen ausgeführt werden.

Das Boundary Scan Prinzip bleibt damit immer gleich, da die externen Module quasi zur natürlichen Schaltung hinzugefügt werden.

Abb.3: Funktionaler Test über externes CION-LX I/O Modul mit Mixed-Signal Kanälen

Über ein derartiges Szenario lassen sich selbst analoge Funktionen, oder Cluster testen. Voraussetzung ist allerdings, dass die I/O Module auch über Mixed-Signal Kanäle verfügen, wie es z.B. beim CION-LX I/O Module von GÖPEL electronic [6] der Fall ist. Zusammenfassend bietet Boundary Scan also von Hause aus schon einige Funktionstestmöglichkeiten, allerdings sind diese auf das statische Niveau begrenzt.

#### Die Funktionstestwelt mal auf den Kopf stellen

Wenn der Begriff Funktionstest in der Produktion fällt, geht die Assoziation als erstes fast immer in Richtung der klassischen Variante – externer Tester ist mit der UUT über die nativen Steckverbinder kontaktiert, fährt seine Sequenzen ab und wertet die Responses aus. Doch es gibt gemäß Tab.2 noch weitere interessante Methoden, welche insbesondere auf den embedded Test fokussiert sind und viele innovative Features aufweisen.

Verfahren Grundlegendes Wirkprinzip Typische Eigenschaften

| Prozessor<br>Emulationstest  | <ul> <li>Ausnutzung der zum Software Debugging integrierten On-Chip Emulation</li> <li>Ansteuerung des Prozessors über das Debug I/F durch einen externen Emulationstester</li> <li>Download von definierter Vektoren in den μP, Test Ausführung und Upload der Responses</li> </ul>                                                      | <ul> <li>Keine Firmware erforderlich</li> <li>automatisierbar</li> <li>At-speed Test</li> <li>Funktionaler Test der gesamten<br/>UUT möglich</li> <li>Diagnose auf Bus /Device Level</li> </ul>                                                                        |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip embedded<br>Instruments | <ul> <li>Permanente Integration von Testinstrumenten in<br/>einen Chip oder Download von Instrumenten als<br/>Soft-IP in einen FPGA</li> <li>Ansteuerung der Instrumente per JTAG durch<br/>einen externen Testcontroller</li> <li>Autonome oder schrittweise Testausführung</li> <li>Upload von Responses oder GO/NOGO Status</li> </ul> | <ul> <li>Keine Firmware erforderlich</li> <li>automatisierbar</li> <li>At-speed Test/Real Time Test</li> <li>Funktionaler Test der mit dem<br/>Instrument verbundenen<br/>Signale/Cluster</li> <li>Diagnose auf Pin/Net/Device<br/>Level, aber auch GO/NOGO</li> </ul> |

| Embedded<br>Operating System | <ul> <li>Download eines kompletten Betriebssystems per<br/>Debug Port oder Booting von einem externen<br/>Speichermedium</li> <li>Steuerung von integrierten Test-, und Diagnostik<br/>Funktionen per JTAG oder UART</li> <li>Autonome Test-Ausführung</li> <li>Upload von Diagnose-Informationen</li> </ul>                              | <ul> <li>Keine Firmware erforderlich</li> <li>konfigurierbar</li> <li>At-speed Test/Real Time Test</li> <li>Funktionaler Test der gesamten<br/>UUT möglich</li> <li>Diagnose auf Bus/Device Level</li> </ul>                                                           |

Tab.2: Funktionale Verfahren zum eingebetteten Testzugriff

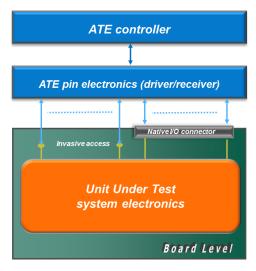

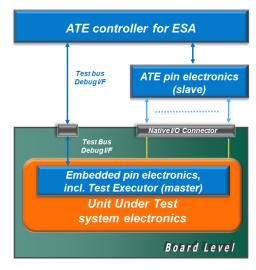

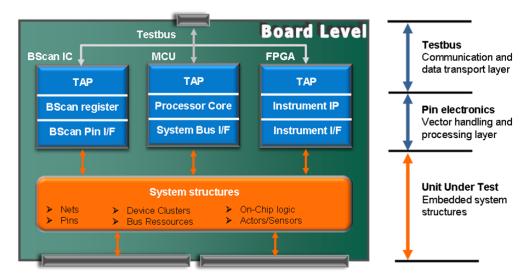

Alle diese Verfahren verfolgen primär ein Ziel – den Anwender von der Codierung eigener Testroutinen durch vorkonfektionierte Lösungen zu entlasten und damit eine wesentlich höhere Effektivität und Kalkulierbarkeit des gesamten Testprozesses zu gewährleisten. Dabei werden die eigentlichen Test-Instrumente ins Innere der UUT verlagert und man spricht vom Embedded System Access. Das hat gemäß Abb.4 weitreichende Folgen.

Scenario for Functional Test, ICT and MDA: **Testing from outside to inside**

Scenario for Embedded System Access:

Testing from inside to outside

#### Pressekontakt:

GÖPEL electronic GmbH Matthias Müller Goeschwitzer Str. 58-60/66 D-07745 Jena Tel: +49-3641-6896-739 Fax: +49-3641-6896-944 E-Mail: press@goepel.com URL: www.goepel.com GÖPEL electronic GmbH • Göschwitzer Str. 58/60 • 07745 Jena, Deutschland

### Abb.4: Paradigmenwechsel beim Test durch eingebetteten Systemzugriff

Die augenscheinlichste Veränderung ist, dass sich die mit Boundary Scan begonnene Transformation von Tester Anteilen weiter verstärkt und nun auch die Testausführungseinheit umfasst. Das heißt es wird noch mehr auf die durch das Design definierten Elemente zurückgegriffen. Das senkt gleichzeitig auch den externen Aufwand.

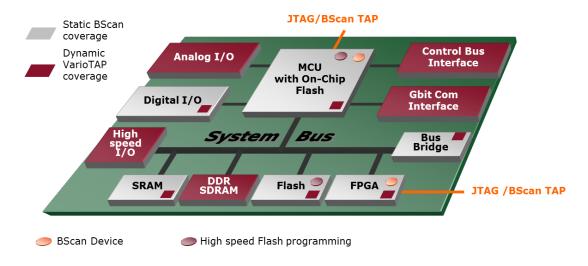

Dabei nutzt der Emulationstest den nativen On-Board Prozessor als Testausführungseinheit und kann dadurch alle an den Core angeschlossenen Elemente erreichen. Typischerweise erfolgt durch den Systembus auch eine natürliche Partitionierung der Gesamtschaltung wodurch sich die Generierungsprozesse auf Basis von Modellen automatisieren lassen.

Abb.5: Partitionsweiser Test durch Prozessor Emulation

Gleichzeitig ermöglicht das Prinzip auch eine schnelle Programmierung von Flash Bausteinen. Dieses sogenannte Core Assisted Programming bietet in vielen Fällen eine wesentlich höhere Performance als Boundary Scan.

Grundsätzlich wird beim Emulationstest der Prozessor von außen mit Vektoren versorgt, legt diese in einem natürlichen Buszyklus an, liest Daten zurück und gibt diese wieder an die übergeordnete Steuereinheit zur Auswertung. Daher gelingt auch nur ein at-speed Test. Neueste Entwicklungen ermöglichen jedoch auch eine Real-Time Abarbeitung von Emulations-Scripts. Als Beispiel sei die von GÖPEL electronic entwickelte VarioTAP® Technologie [7] mit RT-Erweiterung genannt.

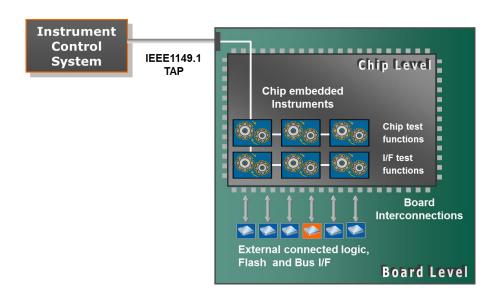

Chip Embedded Instruments finden bereits seit vielen Jahren erfolgreich auf dem Gebiet des Schaltkreis-Tests Verwendung. Dabei werden spezielle IP in das Design fest integriert. Diese Infrastruktur wird durch neueste Standards wie IEEE1687 [8] und IEEE1149.1-2013 [3] nun auch für den funktionalen Boardtest erschlossen. Das Prinzip ist eigentlich recht einfach zu durchschauen und basiert auch auf dem Einsatz von JTAG als Transfermedium (Abb.6).

Abb.6: Ansteuerung von im Chip eingebetteten Instrumenten

Der Vielfältigkeit solcher Instrumente sind in der Praxis de facto keine Grenzen gesetzt. Besonders interessant ist hierbei die Nutzung von FPGA basierenden Instrumenten. Sie werden als Soft-IP temporär in das Target geladen und können individuell an die Testaufgabe angepasst werden. Beispiele für solche Instrumente sind Frequenzmesser, Speichertester, Bit Error Rate Tester, LAN-Tester, Flash-Programmer und Logik-Analyzer um nur einige zu nennen. Allerdings existiert bei FPGA immer das Problem die IP individuell an die jeweiligen Pins der zu testende Schaltung anzupassen. Neueste Entwicklungen wie die von GÖPEL electronic entwickelte ChipVORX Technologie [9] automatisieren jedoch auch diese IP zu Pin Kontaktierung ohne erneute Design-Compilierung.

Interessant ist in diesem Zusammenhang auch der Einsatz von externen I/O Modulen mit FPGA (Abb.7). Sie erweitern auf direktem Weg den Einsatz von FPGA embedded Instruments zum funktionalen Board-Test über Zugriff auf die natürlichen Steckverbinder.

Abb.7: ChipVORX I/O Modul von GÖPEL electronic mit On-Board FPGA

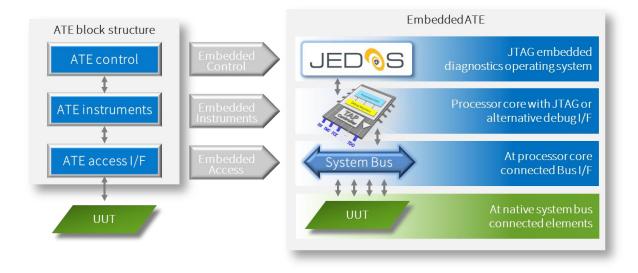

Das dritte bereits in Tabelle 2 ausgewiesene Verfahren ist das eingebettete Betriebssystem zum Test und zur Diagnose. Auch hier wird der Prozessor als Testausführungseinheit genutzt, allerdings unter Kontrolle einer kompletten Test- und Diagnose-Software, wie beispielsweise JEDOS™ (Abb.8).

Abb.8: Einbettung einer kompletten ATE durch ein Test- und Diagnosesystem

Die Software beinhaltet auch bereits vorkonfektionierte Test Vektoren, und Diagnose-Algorithmen, welche prinzipiell in Real Time ausgeführt werden. Der Vektor-Download entfällt komplett. Damit wird der Schritt zu einer vollständig integrierten ATE zum Funktionstest vollzogen.

#### **Getrennt marschieren aber vereint Testen**

Auch wenn die aufgezeigten funktionalen Testverfahren für sich bereits viele neue Möglichkeiten bieten, wird das volle Potential erst durch sinnvolle Kombination erschlossen. Für die JTAG basierenden Verfahren ist dabei von Vorteil, dass sie alle die gleiche Infrastruktur benutzen (Abb. 9). Auf Basis entsprechend Multifunktionaler Systemlösungen wie die von GÖPEL electronic entwickelten JTAG-Plattformen SCANFLEX® und SYSTEM CASCON™ gelingt der interaktive Mix von Struktur- und Funktionstest problemlos.

Abb.9: Einheitliche JTAG-Steuerung von Boundary Scan, FPGA Embedded Instruments und Prozessor Emulation

Für den Produktionsbedarf sind auch komplette Desktop JTAG-Tester, wie z.B. das JULIET System [10], verfügbar (Abb.10). Über integrierte I/O Module mit vielfältigen Funktionstest-Instrumenten und Nadeladaptierung bietet das Gerät eine sehr gute Flexibilität zum umfassenden Test von Prototypen, für Produktionsvolumina im unteren bis mittleren Bereich, sowie für Reparaturen.

Abb.10: Kombinationstester zum synchronisierten Einsatz von externen Instrumenten und sämtlichen Embedded System Access Techniken auf einer Plattform

Darüber hinaus gibt es auch sehr leistungsstarke Plattformen zur offenen, modularen Instrumentierung von klassischen Funktionstestern, welche sich mit entsprechenden Komponenten sehr gut in Richtung Strukturtest konfigurieren lassen. Eine der führenden Integrationsplattformen ist hierbei PXI, bw. PXI Express (Abb11).

Abb.11: PXI/PXIe basierender Kombinationstester, incl MDA Instrumentierung

Der Vorteil solcher Architekturen ist, dass eine sehr hohe Zahl von Multi-Vendor Modulen für nahezu alle Anwendungs- und Leistungsbereiche zur Verfügung steht. Gestützt auf offene Softwarepakete wie LabVIEW™ oder TestStand™ gelingt die Umsetzung flexibler Systemkonzepte. Die Integration der JTAG-Komponenten erfolgt auf Basis von entsprechenden Hardware / Software Plug-Ins. Dabei existieren auch Softwarelösungen, welche dem Funktionstester die volle Kontrolle der JTAG Hardware ermöglichen und ein

interaktives Vektor-Interface bieten. Über diesen transparenten Slave-Mode sind beispielsweise auch Clustertests realisierbar. Zur Integration der Embedded System Access Technologien steht eine ganze Reihe von JTAG Boundary Scan Controllern bereit, alle im natürlichen PXI/PXIe Format und ausgeführt als Single Slot Instrument.

Das gleiche Prinzip des Plug-Ins von JTAG Boundary Scan Komponenten wird im Übrigen auch zur Kombination mit invasiven Testern wie ICT, FPT und MDA verwendet. Auch hier sind interaktive Prozeduren zur Erhöhung der Fehlerabdeckung möglich und sinnvoll.

### **Zusammenfassung und Schlussfolgerungen**

Der immer weiter sinkende Testzugriff erzwingt bei modernen Designs ein Umdenken in der Testphilosophie. Eingebettete strukturelle Tests wie JTAG Boundary Scan in Kombination mit innovativen, eingebetteten funktionalen Testmethoden bieten hier neue Lösungsansätze bis hin zur embedded ATE. Dabei steht vor allem die Verbesserung der Effektivität bei der Testgenerierung unter gleichzeitiger Erhöhung der Testgeschwindigkeit im Fokus. Auf diesem Wege ist es möglich sowohl die Testabdeckung zu maximieren, als auch die Diagnosequalität zu verbessern. Der Einsatz von externen I/O Modulen mit FPGA bietet weitere Möglichkeiten zur einfachen Verbesserung der Testqualität.

Für den Mix der verschiedenen Strategien stehen ausgereifte und leistungsstarke Plattformen zur Verfügung. Das gilt auch für die Kombination mit klassischen, externen Testinstrumenten.

Den Anwendern eröffnet sich damit ein großes Arsenal an technischen Lösungswegen. Die richtige Entscheidung muss aber individuell auf Basis einer genauen Analyse der Produkteigenschaften, der Prozessparameter und nicht zuletzt der Kostensituation getroffen werden.

### Quellen

- [1] IEEE Std.1149.1-1990, Standard Test Access Port and Boundary Scan Architecture

- [2] IEEE Std. 1149.6-2003, Standard for Boundary Scan Testing of Advanced Digital

#### **Networks**

- [3] IEEE Std.1149.1-2013, Standard Test Access Port and Boundary Scan Architecture

- [4] Thomas Wenzel / Andreas Türk Die Crux der BGA-Lötstellen White Paper, GÖPEL electronic, 2014

- [5] Thomas Wenzel / Martin Borowski Einsamer Boundary Scan IC sucht Anschluss White Paper, GÖPEL electronic, 2014

- [6] Thomas Wenzel / J.Heiber Große Teststrategien klein verpackt White Paper, GÖPEL electronic, 2015

- [7] Produktinformation VarioTAP GÖPEL electronic, 2014

- [8] IEEE Std. P1687, standard for Access and Control of Instrumentation Embedded within a Semiconductor Device.

- [9] Produktinformation ChipVORX GÖPEL electronic, 2014

- [10] Produktinformation JULIET Desktop Tester Series2 GÖPEL electronic, 2015