ChipVORX-Technologie für Chip Embedded Instruments auf Intel® MAX® 10 FPGAs erweitert

Neue Modellbibliothek verfügbar

GÖPEL electronic erweitert die Verfügbarkeit der ChipVORX®-Modellbibliotheken auf die FPGAs der Intel® MAX® 10 FPGAs zur Unterstützung von Embedded Test und Embedded Programmierung.

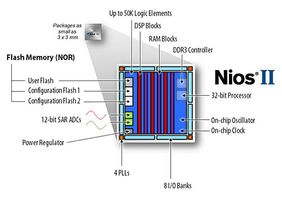

ChipVORX® ist eine von GÖPEL electronic entwickelte Technologie zur universellen Steuerung von Chip-embedded Instruments über den JTAG-Port. Die speziellen ChipVORX®-Modelle sind modulare IP (Intellectual Properties), welche sämtliche relevanten Zugriffsinformationen des jeweiligen Ziel-FPGA enthalten und Teil einer umfassenden IP-Library sind. Anwender können im Rahmen einer Projektentwicklung zunächst den Ziel-FPGA auswählen und anschließend die gewünschte Test- oder Programmierfunktion aktivieren. Dazu gehören Flash-Programmierung (für parallele oder serielle NOR-Flash, inklusive FPGA Boot-Flash), RAM Access Test, universelle Frequenzmessung sowie Bit Error Rate Test (BERT). Die ChipVORX®-Technologie ermöglicht dem Anwender die Realisierung des Embedded System Access (ESA).

Die Intel® MAX® 10 FPGAs basieren auf einer 55 nm Embedded NOR Flash Technologie. Der Controller wird in verschiedenen Gehäuseformen und Größen mit bis zu 672 Pins geliefert und über das JTAG-Interface adaptiert. Durch designintegrierte Testelektronik entfallen Kontaktierungen der UUT über Nadeln oder Proben. Zudem ist ein Mix mit anderen non-intrusiven Verfahren wie Boundary Scan oder Processor Emulation problemlos auf einer Plattform möglich. Applikationseinstellungen für die Inhalte (einschließlich der Verbindung zwischen IP und Pin) erfolgen automatisch und ohne FPGA-Synthese. Parameter für Funktionen wie Bit Error Rate Test und Frequenzmessung sind interaktiv über Steuerpanels einstellbar und werden sofort wirksam. Die ChipVORX® Modellbibliotheken ermöglichen eine schnelle Systemadaption mit vereinheitlichtem Equipment für sämtliche Test- und Programmieraufgaben. Dabei verbessern sie die gesamte Prozesseffektivität, schützen Investitionen und sind gegenüber externen Testern deutlich preisgünstiger.

Kontakt

Kontakt