Simplified Testing and Programming of Cypress PSoC 4 Controllers with VarioTAP technology

Design Validation and Prototype Testing without Firmware

GOEPEL electronic extends the VarioTAP model range to include Cypress PSoC 4 controllers.

The VarioTAP model libraries allow a complete fusion of Boundary Scan test and JTAG emulation. The processor is controlled via the native debug port, allowing users to perform hardware design validation and prototype testing without firmware. In addition, the method also offers options for dynamic testing and accelerated in-system programming of Flash.

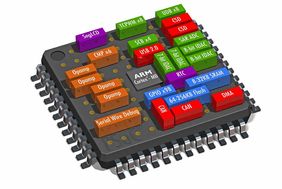

The Cypress programmable System-on-Chip architectures (PSoC) are equipped with ARM Cortex-M0 cores. The internal peripherals can be addressed via the SWD interface, GPIOs can be controlled, custom IPs can be loaded and the internal Flash can be programmed and verified. The main field of application for the controller family is LowPower, Human Machine Interface (HMI) and Wireless Connectivity, combined with programmable analog and digital blocks.

VarioTAP is a technology that utilizes design embedded processors as intelligent control units for versatile test and programming operations. The technology does not require any firmware. The processor’s native debug port is used for external control, supporting JTAG as well as additional protocols.

联系我们

联系我们