# Viele Fliegen mit einer Klappe: Embedded-Elektronik testen und programmieren mit geringem Zugriff

Das Problem des Testens ist so alt wie der Transistor selbst. Anfangs wurde ausschließlich über die nativen Steckverbinder auf den Prüfling zugegriffen. Später dominierte der sogenannte Intrusive Board Access (IBA) in Form des In-Circuit-Test (ICT) und des Flying Probe Test (FPT). Diese Testverfahren sind heute häufig im Einsatz, stoßen aber beim Einsatz an Ball Grid Arrays (BGA), Chip Scale Packages (CSP) und kleinsten Bauformen wie 01005 an ihre Grenzen. Nicht nur mangelt es modernen Baugruppen an Platz, um alle Signale mit Nadeln zu kontaktieren, auch aufgrund negativer Einflüsse auf die Signalqualität fällt es immer schwerer, mit herkömmlichen Methoden zu Testen. Das stellt Entwickler bereits während des Designs neuer Baugruppen vor extreme Herausforderungen.

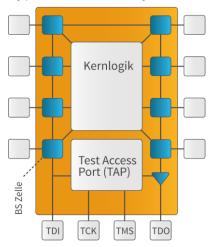

War der In-Circuit-Test über viele Jahre die dominante Testmethode, so wurde die sogenannte Pin-Elektronik eines Testers aufgrund des kontinuierlich sinkenden Testzugriffs mehr und mehr in die zu testende Schaltung verlagert. Als Folge entstand eine designintegrierte Pin-Elektronik, welche per JTAG-Testbus angesteuert wird. Dies ist der Ansatz des Boundary Scan (IEEE Std. 1149.x), wobei die offene Erweiterbarkeit der Registerarchitektur sowie die Universalität des Bus-Interfaces und seinem Übertragungsprotokoll das eigentlich Geniale sind. Diese Eigenschaften machen Boundary Scan bis

heute zu einer technologischen Basis für neue nicht-intrusive Verfahren und Standards zum Testen, Debuggen, Programmieren und Emulieren. Eine Tatsache, die das Ensemble der Zugriffsstrategien auf Board-Level nachhaltig verändert hat.

# Typischer Boundary Scan IC

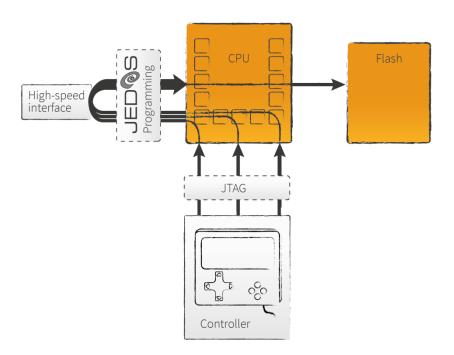

Abb.1: Typischer Aufbau eines Boundary Scan IC

#### Weit mehr als nur Boundary Scan

Ein grundlegender Testansatz ist die Verifikation von einwandfreien Boardverbindungen.

Der Boundary Scan-Zugriff über das JTAG-Interface ist inzwischen ein Klassiker. Über die standardisierte Schnittstelle wird der Zugriff auf eine serielle Schiebekette hergestellt, über die sämtliche Boundary Scan IOs gesetzt und ausgelesen werden können. Weiterhin ist es möglich, Kurzschlüsse, nicht gelötete Pins oder auch Pull-Widerstände zu finden.

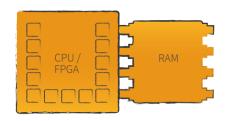

Das Potenzial dieses Zugriffs ist noch größer: Die Technologien können auch genutzt werden, um einen RAM Verbindungstest auszuführen. Dabei werden sämtliche Adress-, Daten- und Steuerleitungen mit fest definierten Testmustern angesprochen. Mithilfe dieser Testmuster lassen sich pingenaue Fehleraussagen bezüglich der korrekten Verbindung zwischen Controller und RAM-Baustein treffen.

Ebenso kann die Verbindung zu externen FLASH Bausteinen und Elementen mit einem seriellen Interface (z.B.: I<sup>2</sup>C, SPI, MIDO, ...) überprüft werden. Dazu werden ebenfalls sämtliche Adress-, Daten- und Steuerleitungen angesprochen und so zum Beispiel die Device und Hersteller ID ausgelesen und ausgewertet. Auf diesem Weg wird die korrekte Bestückung, sowie eine einwandfreie Verbindung verifiziert. Bei I<sup>2</sup>C Bausteinen reicht es sogar schon aus, anhand der Device Address das korrekte Acknowledge des angesprochenen Bausteins zu überprüfen.

Auf modernen Baugruppen kommen verschiedenste Schnittstellen zum Einsatz, welche überprüft werden müssen. Beispielsweise lassen sich digitale, aber auch analoge IOS, sowie funktionale Schnittstellen (z.B.: CAN oder LIN), mit einfacher Adaptionen testen. Alle genannten Testmöglichkeiten, die

auf dem Zugriff über die JTAG-Schnittstelle beruhen, können als "Embedded Board Test" zusammengefasst werden.

## Das Board auf Herz und Nieren prüfen

Heutige Teststrategien erfordern mittlerweile mehr als das einfache Prüfen von Boardverbindungen. Neben der einwandfreien Kontaktierung muss vor allem auch die Board- und Bauteilfunktion getestet werden.

So lassen sich diverse On-Board-Instrumente ansprechen und auswerten. Lage- und Temperatursensoren, ADCs, DACs und verschiedenste Transceiver verfügen über standardisierte Schnittstellen zur Konfiguration. Ebendiese Schnittstellen (z.B. I<sup>2</sup>C) werden nun genutzt, um durch einfache Lese- und Schreibzugriffe auf die Register zuzugreifen. So lässt sich zum Beispiel der aktuelle Winkel eines Lagesensors, die Temperatur oder auch der anliegende Spannungswert eines ADCs erfassen und auswerten. Die Funktion der verschiedenen Bauteile wird entsprechend überprüft.

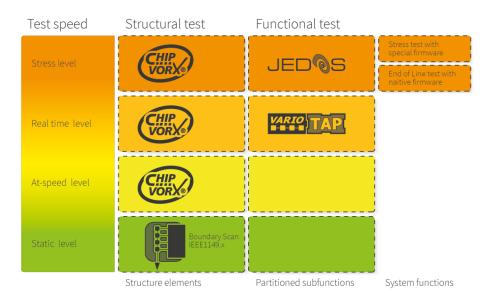

Mithilfe verschiedener Technologien lassen sich zudem die On-Chip-Instrumente überprüfen. Eine solche Technologie ist JEDOS (JTAG Embedded Diagnostic Operating System) von GÖPEL electronic. Damit wird ein vollständiges Testsystem, inklusive Testpattern und Diagnose-Tools, auf den Microcontroller geladen und ausgeführt. So entfällt die Notwendigkeit des Datenaustauschs zwischen Software und Prüfling während des Testens. Der Test läuft somit vollständig auf dem Prüfling ab und kann mit voller Geschwindigkeit ausgeführt werden. Als Beispiel dient ein RAM-Test. Dieser wird (im Gegensatz zum Boundary Scan) mit dem "echten" RAM-Interface ausgeführt, wodurch dessen Funktion nachgewiesen wird. Der Test unter voller Geschwindigkeit erlaubt zusätzliche Funktionen wie einen RAM Stress-Test, bei dem die Funktion auch unter extremer Belastung überprüft wird.

Abb.2: Speicher- und Verbindungstest

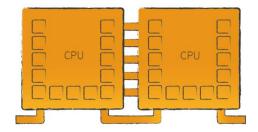

Auch Schnittstellen können funktional überprüft werden. So können die Ressourcen auf dem Board genutzt werden, um zum Beispiel eine USB-Host-Slave-Kommunikation anzustoßen und zu überprüfen. Durch den Debug-Zugriff auf den Controller (z.B. Emulationstechnik VarioTAP oder JEDOS) werden die Schnittstellen auf dem Prüfling entsprechend konfiguriert und die Kommunikation angestoßen. Auf diesem Weg lassen sich auch Ethernet, CAN, LIN und weitere Schnittstellen funktional überprüfen. Darüber hinaus ist anhand bestimmter FPGA-Designs (z.B. ChipVORX) auch eine qualitative

Aussage zu High Speed Interfaces zu treffen. Hierzu kann ein Bit Error Rate Test durchgeführt oder ein Augendiagramm aufgenommen und ausgewertet werden. GÖPEL electronic führt all diese Technologien unter dem Begriff "Embedded Functional Test".

Abb.3: Übersicht Testgeschwindigkeit und Testtiefe der Embedded JTAG Solutions Technologien

#### Schnell Programmieren trotz geringem Zugriff

Neben dem Verifizieren und Testen der Funktion eines Prüflings, ist auch das Programmieren verschiedenster Daten eine große Herausforderung, ganz gleich ob in Entwicklung oder Produktion. Vor allem zunehmende Dateigrößen und wachsende Ansprüche an die Programmiergeschwindigkeit stellen eine große Hürde dar. GÖPEL electronic vereint verschiedene Technologien unter dem System "Embedded Programming".

Boundary Scan kann dafür genutzt werden, wenn nur kleine Datenmengen programmiert oder keine besonderen Anforderungen an die Testdauer gestellt werden. Vor allem das Programmieren von Seriennummern und einfachen Fertigungsdaten lässt sich auf diesem Weg sehr gut umsetzen.

Bei zunehmender Datengröße oder sinkender Testdauer können alternative Zugriffstechnologien (z.B.: VarioTAP) zum Einsatz kommen. Da nun keine serielle Schiebekette für den Datentransfer genutzt wird, lassen sich deutlich höhere Programmiergeschwindigkeiten erreichen. Auch On-Chip-Flash-Speicher können über den Debug-Zugriff programmiert werden.

Der höchste Datendurchsatz wird mit JEDOS erreicht. Vor allem in Verbindung mit zusätzlichen Schnittstellen ist die maximale Programmiergeschwindigkeit nur noch die verwendeten Bausteine limitiert. So erlaubt JEDOS zum Beispiel das Streamen von Daten über eine Ethernet-Schnittstelle. Via LAN werden die Programmierdaten auf den Prüfling geladen und in den FLASH geschrieben. Es erfolgt keinerlei Datenaustausch über das JTAG Interface. Das Laden von Programmierdaten ist so auch von SD Karten möglich.

Abb.4: Programmierung mit JEDOS

### Nichts geht ohne Hardware

Um die vielfältigen Test- und Programmiermöglichkeiten vollständig in die Praxis umzusetzen bedarf es einer leistungsfähigen Hard- und Softwareplattform. Als Schnittstelle zwischen PC und Prüfling dient der Boundary Scan Controller. Diese verarbeitet die von der Software generierten Testmuster und leitet sie über die Debug-Schnittstelle an den Prüfling weiter. Der SCANFLEX II Cube Controller ist eine frei erweiterbare Hardwarelösung, die alle benötigten Schnittstellen zum Prüfling zur Verfügung stellt. Die System CASCON Software kann dann genutzt werden, um sämtliche Soft- und Hardwarefunktionen für den endgültigen Test zu konfigurieren.

Egal welches Hard- und Software Komponenten oder Technologien Sie nutzen wollen, die Embedded JTAG Solutions lassen sich frei miteinander kombinieren, um so die bestmögliche Testabdeckung zu erreichen.

Abb.5: SCANFLEX II Cube (JTAG/Boundary Scan Controller)

# Zusammenfassung

Alle beschriebenen Test- und Programmierstrategien, sowie die zugehörigen Soft- und Hardwarelösungen fasst Göpel electronic unter dem Begriff "Embedded JTAG Solutions" zusammen. Die standardisierte JTAG Schnittstelle, aber auch andere Debug-Interfaces, erlauben den Einsatz der EJS während des gesamten Produktlebenszyklus.

Abb.6: Elektronik-Produktlebenszyklus

Schon in der Design-Phase können Lücken in der Testabdeckung identifiziert und durch wenige Anpassungen beseitigt werden. Dafür steht bereits ein reichhaltiger Fundus an Designrichtlinien zum Maximieren der Testmöglichkeiten zur Verfügung. Da Boundary Scan direkten Zugriff auf die Pin-Elektronik gewährt, kann das Verhalten der Baugruppe bereits ohne Firmware überprüft werden. Aber nicht nur die Hardware kann auf diesem Weg bereits im Prototypen-Status getestet werden. Dank der verschiedenen Programmierlösungen lassen sich auch erste Firmware-Versionen überprüfen.

Kommen die Embedded JTAG Solutions bereits an Prototypen zum Einsatz, lassen sich die verschiedenen Testroutinen ohne größere Aufwände in die Produktion überführen. Durch das Anpassen weniger Parameter können die schon vorher verifizierten Zugriffe übernommen werden. Aber auch Reparaturen werden erleichtert. Zunächst reduziert das JTAG-Interface die Anzahl der zu kontaktierenden Signale. Weiterhin erfolgt die Diagnose immer aus "Prüflingssicht", weshalb Diagnosemeldungen sehr genau ausgegeben werden können. Die Fehlerursache wird eindeutiger und vor allem schneller gefunden.

Somit zeigt sich, dass die bewährte JTAG-Schnittstelle viel mehr leisten kann als nur den klassischen JTAG/Boundary Scan. Mit den Embedded JTAG Solutions kann Testen und Programmieren jede Phase des Produktlebenszyklus entscheidend vereinfacht und beschleunigt werden.

#### Autoren:

Alexander Labrada Diaz, Applikationsingenieur im Bereich Embedded JTAG Solutions bei der Göpel electronic Gmbh:

Matthias Müller, Public Relations Manager bei der Göpel electronic GmbH

Tel.: +49 (0)3641-6896-739

Fax: +49 (0)3641-6896-944

E-Mail: presse@goepel.com

Internet: www.goepel.com